This project is an advance upon my initial PET 2001 clone computer built in 2018. It is another 40-column, non-CRTC, 2001 or 3000-series PET clone with a lot of functionality that the original, unexpanded computer never had.

This project is currently in the PCB-layout phase. I have completed the schematic entry and the full, preliminary schematics are presented in the project document PDF linked-to immediately above.

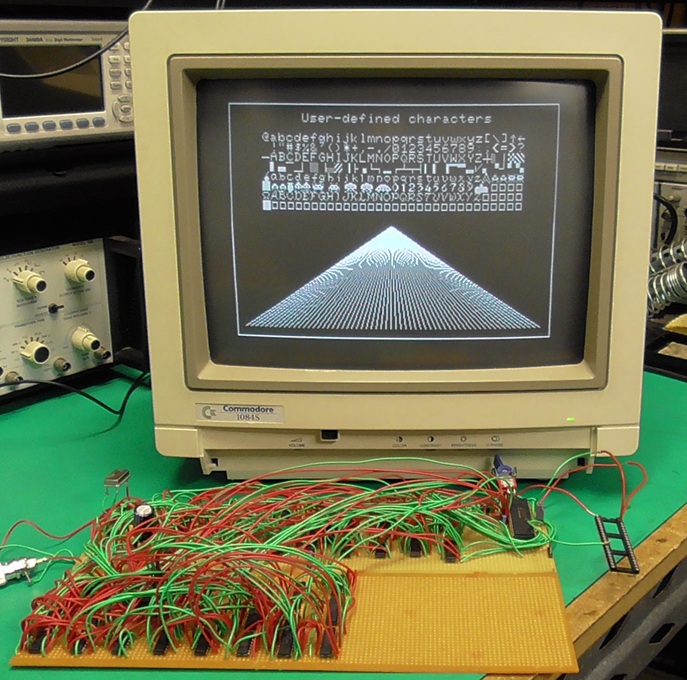

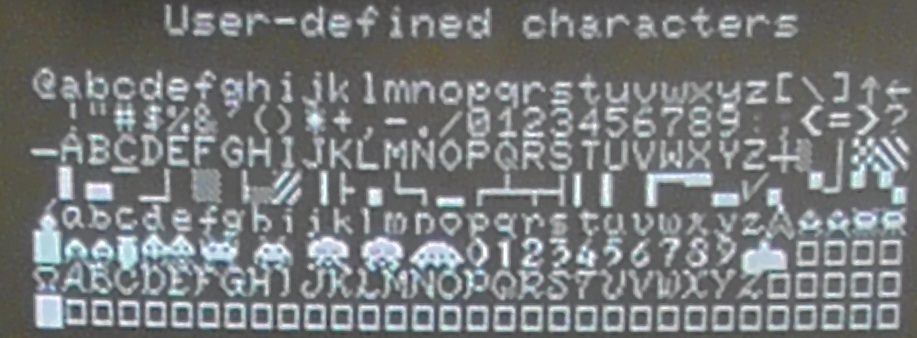

At the time of writing, I have only physically prototyped and verified the entirety of the video graphics generation hardware. Aside from the memory chips, the video generator circuitry that I have designed is composed entirely of 74HC and 74HCT-series discrete logic. This is the most complex part of the computer, and the whole of it was assembled on veroboard, as shown and detailed in the project document.

I do not intend to veroboard the entire computer. As I immediately needed some kind of readily accessible and practically programmable CPU (so as to not waste eons of time) to program the video memories and thus produce some form of test graphics on screen, I plonked a PIC16F874 microcontroller onto the veroboard and wired it to the video generator hardware control lines, data and address busses. The test program for the PIC was written in C and is given in the project document.

All the video graphics screen-shots shown, taken from my Commodore 1084S monitor, were generated by this veroboard video hardware.

The main features of this new PET computer design are:

That is enough RAM to play approximately 13 seconds of sampled speech through the audio DAC at a sampling rate of 8kHz!